| American Journal of Engineering Research (AJER) | 2018           |

|-------------------------------------------------|----------------|

| American Journal of Engineering Research (AJER) |                |

| e-ISSN: 2320-0847 p-ISSN : 2320-0936            |                |

| Volume-7, Issue-                                | -9, pp-132-140 |

|                                                 | www.ajer.org   |

| Research PaperOp                                | en Access      |

# Data Placement Algorithm For Power Consumption Reduction in Field Programmable Gate Array

Mohd.Qutubuddin<sup>1</sup>, Prof.Dr.G.Manoj Someswar<sup>2</sup>

Research Scholar, VBS Purvanchal University, Jaunpur, U.P., India Research Supervisor, VBS Purvanchal University, Jaunpur, U.P., India Corresponding Author: Mohd.Qutubuddin

ABSTRACT; There was a great increase for the beyond few years in the subject of embedded systems, especially in the patron electronics phase. The growing demand towards excessive overall performance and occasional electricity systems has compelled researchers to come up with progressive design methodologies and architectures that could obtain these objectives and meet the stringent system necessities. lots of those systems perform a few sort of streaming records processing that requires the sizeable arithmetic calculations.FPGAs are being more and more used for a selection of computationally intensive packages, in particular in the realm of digital sign processing (DSP). due to rapid will increase in fabrication generation, the present day technology of FPGAs consists of a large quantity of configurable common sense blocks (CLBs) and numerous other capabilities such as on-chip reminiscence, DSP blocks, clock synthesizers, and many others. to aid enforcing a huge range of mathematics packages. The excessive non-recurring engineering (NRE) costs and long improvement time for application unique incorporated circuits (ASICs) make FPGAs appealing for application unique DSP solutions.

Despite the fact that the present day generation of FPGAs gives variety of resources along with logic blocks, embedded memories or DSP blocks, there may be nonetheless predicament on the quantity of those assets being offered on each tool. then again, a blended DSP/FPGA layout flow introduces several challenges to the designers because of the combination of the design tools and complexity of the algorithms. therefore, any attempt to simplify the design waft and optimize the processes for both location or performance is liked.

This research paper develops innovative architectures and methodologies to exploit FPGA assets efficiently. in particular, it introduces an green approach of imposing FIR filters on FPGAs that can be used as primary constructing blocks to make various styles of DSP filters. Secondly, it introduces a novel implementation of correlation function (the use of embedded memory) this is hugely utilized in photo processing packages. moreover, it introduces an ultimate facts placement algorithm for energy consumption reduction on FPGA embedded memory blocks. those strategies are extra green in terms of electricity intake, performance and FPGA vicinity and they may be incorporated into some of signal processing programs. some real life case studies also are furnished in which the above strategies are implemented and good sized performance is accomplished over software primarily based algorithms. The consequences of such implementations also are in comparison with competing techniques and exchange-offs are discussed. in the end, the challenges and recommendations of integrating such methods of optimizations into FPGA design tools are discussed.

**KEYWORDS:** configurable logic blocks (CLBs), non-recurring engineering (NRE), digital signal processing (DSP), clock organization tiles (CMTs)

Date of Submission: 31-08-2018Date of acceptance: 15-09-2018

### I. INTRODUCTION

### Present day FPGAs give the accompanying components:

**Configurable method of reasoning squares:** To offer abilities to executing basis works and registers. **On-chip memory:** To give on-chip accumulating Hard vast scale ensured advancement (IP) focuses, for instance, (Ethernet MAC, Transceivers, Multipliers, DSP squares, ...): To give viable complex limits **Clock organization resources:** Clock dissemination and repeat association and clock moving capacities. **Info/Output pieces:** To give the interface to outside world.

Coordinating resources: To give interconnectivity among all method of reasoning squares and hard macros.

www.ajer.org

Embedded processors: To give dealing with control either as a sensitive or simple.

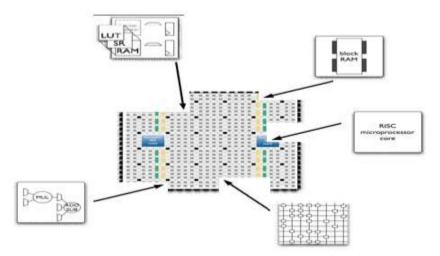

Figure 1 outlines an ordinary FPGA plan with the basic building pieces. As it can be seen from the figure, the square memories are bits of RAMs open on chip and don't expend away room from the method of reasoning pieces. Realize that investigate tables (LUTs) inside the method of reasoning impedes that are dominatingly utilized to influence combinational reason, to can similarly be organized as RAMs or move registers. This is an amazingly capable technique for making shift registers without using the limit segments.

Figure 1: General FPGA architecture

#### Xilinx Virtex 5 Family Architecture Overview

The Virtex 5 family gives the most recent and proficient components inside Xilinx FPGA families. The Virtex 5 family contains five undeniable sub-families.[1] Each stage contains a substitute extent of components to address the necessities of a wide arrangement of bleeding edge reason designs. Despite the most dynamic, world class basis surface, Virtex 5 FPGAs contain some hard-IP system level squares, including serious 36-Kbit piece RAM/FIFOs, second period 25x18 DSP cuts, enhanced clock organization tiles with fused modernized clock head (DCM) and stage darted circle (PLL) clock generators, and impelled setup options.

Additional stage dependant segments consolidate control propelled fast serial handset impedes for enhanced serial accessibility, tri-mode Ethernet MACs (Media Access Controllers), and first class PowerPC 440 chip introduced in-your-confront squares. These segments allow moved basis fashioners to create the biggest measures of execution and handiness into their FPGA based systems. In view of a 65 nm best in class copper handle advancement,[2] Virtex 5 FPGAs are a programmable differentiating alternative to custom ASIC development. The Virtex-5 LX,

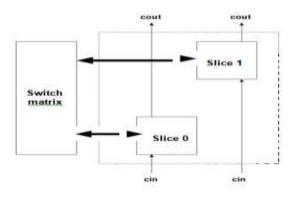

LXT, SXT, FXT, and TXT stages are improved for unrivaled basis, world class method of reasoning with low power system, DSP and low power serial accessibility, embedded taking care of with quick serial accessibility, and ultra high information transmission independently. The CLBs are the principal reason resources for completing sequential and furthermore combinatorial circuits. Each CLB part is related with a switch organize for get to the general coordinating lattice as showed up in Figure 2. A CLB part contains two or three cuts. These two cuts don't have direct relationship with each other. Each cut in a fragment has a free pass on chain.[3]

### Figure 2: FPGA configurable logic block

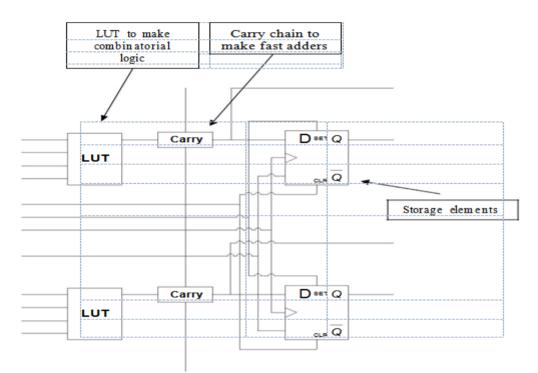

Each cut contains four method of reasoning investigate tables (LUTs), four storing segments, wide limit multiplexers, and pass on basis. These segments are used by all slices to give basis, calculating, and ROM limits. Furthermore, a couple of cuts support two additional limits: securing data using appropriated RAM and moving data with 32-bit registers. Cuts that reinforce these additional limits are called SLICEM (M for memory), and others are called SLICEL (L for basis). Figure 3 depicts the point by point building of each cut in CLBs. LUTs can execute any limit that is mix of 4 data sources. There are a couple of controlling multiplexers that can give the system among neighboring justification resources.[4] Yield of each LUT could be enrolled or non-enlisted. The pass on chain compose inside the CLB structure gives the directing resources for make fast adders. This is an extraordinary coordinating resource that is separate from general directing resources among CLBs. Furthermore a couple of multiplexers solidify the yields of the LUTs or neighboring CLBs as showed up in Figure 3

### Figure 3: Slice detailed structure

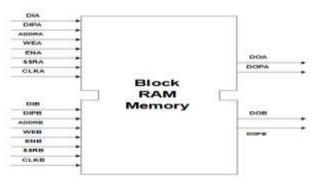

Virtex 5 devices feature a considerable number of 36 Kb square RAMs. Each 36 Kb square RAM contains two self-governing controlled 18 Kb RAMs. Square RAMs are set in portions, and the total number of piece RAM memory depends on upon the traverse of the Virtex 5 device.[5] The 36 Kb pieces are cascadable to enable a more significant and more broad memory execution, with an irrelevant arranging discipline. Figure 4 shows a cascadable square RAM with two specific read and make ports. Embedded twofold or single port RAM modules, ROM modules, synchronous FIFOs, and data width converters are easily completed using the Xilinx focus generator contraption and fundamental RAM squares.

Figure 4: Dual port cascadable block RAM

Make and read activities are synchronous. The two ports are symmetrical and totally independent, sharing only the set away data. Each port can be orchestrated in one of the available widths, free of the other port. Besides, the read port width can be not the same as the create port width for each port. The memory substance can be instated or cleared by the outline bit stream. In the midst of a make activity the memory can be set to have the data yield either remain unaltered, reflect the new data being created, or the past data presently being overwritten.

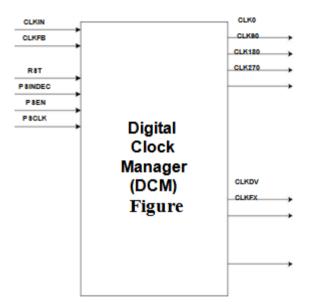

The clock organization tiles (CMTs) in the Virtex 5 family give to a great degree versatile and first class timing. Each CMT contains two mechanized clock boss (DCMs) and one arranged jolt circle (PLL). Figure 5 shows an unraveled point of view of the DCM which offers clock organization features.

Figure 5: DCM primitive block inside CMT

The Virtex 5 DSP cut fuses a wide 25x18 multiplier and an incorporate/subtract work that has been connected with fill in as a basis unit. This reason unit can play out a large group of bitwise cognizant tasks when the multiplier isn't used. The DSP cut consolidates an illustration pointer and a case bar discoverer that can be used for joined altering, surge/sub-current disclosure for drenching number juggling, and auto resetting counters/gatherers.[6,7] A bit of the indispensable components of these DSP cuts are according to the accompanying:

### 25 x 18 multiplier

Semi-unreservedly selectable pipelining among direct and course ways aggregators/adders/subtracters in two DSP48E cuts Single Instruction Multiple Data (SIMD) Mode for three-input wind/subtracter Optional data, pipeline, and yield/gather registers

### Xilinx FPGA Design Flow

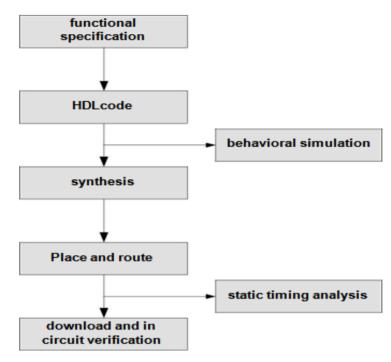

Figure 6 shows the Xilinx FPGA setup stream that contains the going with strides: functional specific of the structure, layout entry in gear delineation vernacular, for instance, VHDL or Verilog, design amalgamation, plot use (place and course), contraption programming, in conclusion in circuit check. Blueprint affirmation, which fuses both useful check and timing check, takes places at different concentrations in the midst of the arrangement stream.

The going with delineates what ought to be done in the midst of every movement.

Figure 6: FPGA design flow

The underlying advance incorporates examination of the arrangement essentials, issue crumbling, diagram entry and viable entertainment where exactness by taking a gander at yields of the HDL show and the conduct display is checked. Mix incorporates the difference in a HDL delineation to a netlist which is basically an entryway level depiction of the arrangement.[8] In the midst of this movement, diverse improvement constraints can be associated with the blueprint. In use of the diagram, the made netlist is mapped onto particular contraption's inside structure using development libraries. The standard time of the execution arrange is place and course, which designates FPGA resources, (for instance, method of reasoning cells, memory, in-your-confront squares, and affiliation wires). By then these plan data are formed to an excellent archive by a program called bit stream. In the midst of the arranging examination exceptional programming checks whether the executed diagram satisfies timing confinements showed by the customer. In this movement, the veritable put off models are used to check the real deferral on the chip in the wake of directing.

#### **DSP Design Flow/Tools on FPGAs**

Working up a methodology for the hardware execution of complex DSP applications on a reconfigurable justification could be a trying task in view of the compromise of a couple of plan gadgets required at the same time.[10] A champion among the most troublesome methods in structure arrangement is perceiving a starting stage! Frameworks empower us to manage complex diagrams adequately, confine design time, discard numerous wellsprings of slip-ups, constrain the work anticipated that would complete the arrangement, and generally make perfect course of action plots. The upsides of taking after such a rationality absolutely surpass its headway costs.[9]

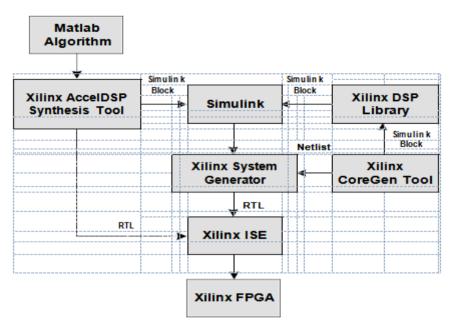

Planning DSP calculations on FPGAs is a very difficult errand. The regular way of DSP calculations is to utilize programming based dialects, for example, C and execute the calculations on DSP processors. FPGAs utilize equipment depiction dialect (HDL) to do a similar errand. The change of a product based calculation to equipment is a robotized procedure more often than not. Be that as it may, the DSP calculations could be planned in HDL from the earliest starting point with unique mastery. Figure 7 demonstrates the DSP outline stream on FPGAs utilizing a few instruments offered by Xilinx. A MATLAB calculation can be changed over to register exchange level (RTL) utilizing AccelDSP configuration apparatuses or it can be joined with Simulink squares. Xilinx gives a DSP library to actualize complex DSP calculations, for example, channels that can be utilized as a part of any outline. Likewise, Xilinx coregen device can be utilized to make complex DSP works in RTL. Coregen is a parameterized instrument that can create complex capacities. A Simulink configuration can be changed over to RTL consequently utilizing System generator apparatus. Regardless, a RTL based plan can be made that can be set and steered utilizing Xilinx ISE apparatus set. This can make the bit stream expected to design the FPGA.

2018

Figure 7: FPGA/DSP design flow

#### Xilinx System Generator Tool

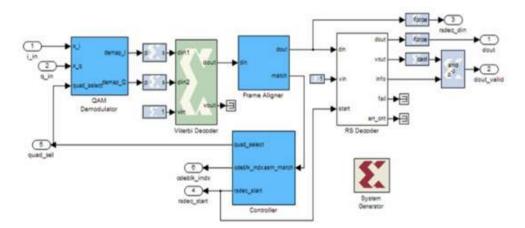

System Generator is a DSP design gadget from Xilinx that enables the use of The Math works indicate based framework condition Simulink for FPGA design.[11] Plans are gotten in the DSP big-hearted Simulink showing condition using a Xilinx specific blockset. Xilinx Simulink blockset is a significantly parameterized library that fuses DSP limits and estimations. In excess of 90 DSP building squares are given in the Xilinx DSP blockset for Simulink. These pieces join the essential DSP building squares, for instance, adders, multipliers, and registers.[12] Similarly included are a plan of complex DSP building squares, for instance, forward botch change pieces, FFTs, channels, and memories. These pieces utilize the Xilinx IP focus generators to pass on enhanced results for the picked device. Figure 2.8 shows a delineation of a Simulink DSP arrange for that instantiates DSP squares.[13]

Figure 8: A snapshot of a Simulink DSP design. This block diagram can be converted to RTL using System Generator software

Programming normally changes over the strange state system DSP piece layout to RTL. The result can be joined to Xilinx FPGA development using ISE instruments.[14] Most of the downstream FPGA use steps including mix and place and course are thus performed to make a FPGA programming archive.

System Generator gives a structure joining stage to the arrangement of DSP on FPGAs that allows the RTL, Simulink, MATLAB, and C/C++ fragments of a DSP structure to get together in a single multiplication and utilization condition. System Generator supports a disclosure piece that empowers RTL to be outside made into Simulink and co-reenacted. System Generator moreover supports the thought of a MicroBlaze embedded processor running C/C++ programs.

*2018*

DSP building pieces are given in the Xilinx DSP blockset for Simulink.[15] These pieces incorporate the normal DSP building squares, for example, adders, multipliers, and registers. Additionally included are an arrangement of complex DSP building pieces, for example, forward mistake amendment squares, FFTs, channels and recollections. These squares use the Xilinx IP center generators to convey enhanced outcomes for the chose gadget.

### Xilinx AccelDSP Tool

Algorithmic MATLAB models can be solidified into System Generator through AccelDSP. AccelDSP consolidates viable algorithmic blend that takes floating point MATLAB as data and produces a totally arranged settled point appear for use with System Generator. Features consolidate skimming to settled point change, customized IP incorporation, diagram examination, and algorithmic booking.

AccelDSP mix gadget is the principle DSP mix instrument that empowers the maker to change a MATLAB skimming point layout into a hardware module that can be completed in a Xilinx FPGA. The AccelDSP association device incorporates a graphical UI that controls an organized circumstance with other arrangement gadgets, for instance, MATLAB, Xilinx ISE [56] gadgets, and other industry standard HDL test frameworks and method of reasoning synthesizers. AccelDSP Synthesis gives the going with limit:

Examines and researches a MATLAB skimming point plot

Therefore makes a relative MATLAB settled point plot

Summons a MATLAB propagation to check the settled point design

Enables to research arrangement trade offs of counts that are enhanced for the target FPGA plans

Makes a synthesizable RTL HDL show and a test bench

RTL reason synthesizers, and Xilinx ISE use instruments

There are three mix streams in AcceDSP instrument: The default amalgamation stream is to make an execution using ISE programming and affirm the layout using HDL entryway level diversion. The second stream is the System Generator stream. In this stream, the diagram is changed over into a System Generator impede that can be consolidated into a greater System Generator design. The third stream is gear co-reenactment stream that uses the hardware stages, for instance, Virtex 4/5 phases.

### Simulink

Simulink is an item mechanical assembly from MATLAB for showing, reenacting, and separating great systems. The Xilinx System Generator continues running as a component of Simulink. The System Generator segments bundled as the Xilinx Block set, appear in the Simulink library program. Structure Generator works inside the Simulink demonstrate based framework logic. Oftentimes an executable specific is made using the standard Simulink square sets. This assurance can be formed using skimming point numerical precision and without gear detail. Once the value and crucial dataflow issues have been portrayed, System Generator can be used to demonstrate the hardware utilization purposes of enthusiasm for specific Xilinx contraption. Structure Generator to deliver extremely enhanced netlists for the DSP building squares. Structure Generator can execute all the downstream utilization instruments to thing a bit stream for programming the FPGA. An optional testbench can be made using test vectors expelled from the Simulink condition for use with the test framework.

### Software Based High Level Design Tools

Notwithstanding the purposes of premium, one reason that FPGAs have not yet found more broad affirmation in the DSP applications is the nonattendance of an item based arrangement stream, (for instance, C) that does not require learning of FPGA building nor gear portrayal vernacular (HDL). Genuinely, DSP programming engineers imagine that its to a great degree troublesome with respect to the hardware execution and this ends up being more troublesome while looking for and FPGA course of action. There have been a couple of choices that help the diagram stream issues by melding a C-based arrangement stream elective that mirrors the standard DSP design stream. These instruments ought to modernize the technique of change of programming based plans to gear vernaculars anyway there are up 'til now various confinements to the extent how to create code with the end goal that makes this move steady. For example, recursive limits can't be up 'til now changed over to gear using these gadgets. In the going with, an anomalous state chart of these instruments is shown.

### MATLAB

MATLAB is an unusual state particular enrolling vernacular and figuring headway mechanical assembly that can be used as a piece of a couple of uses, for instance, data portrayal/examination, numerical examination, signal taking care of, control design, et cetera. Using the MATLAB programming, course of action can be proficient snappier than standard programming tongues, for instance, C, C++. Extra toolboxs are an

aggregations of uncommon reason MATLAB limits that are available freely. These item fixes stretch out the MATLAB capacities to deal with particular classes of issues in these application districts. MATLAB gives different components, of which the most basic ones are:

Headway condition for regulating code, records, and data

Shrewd gadgets for iterative examination, plot, and basic reasoning

Logical capacities with regards to coordinate polynomial math, bits of knowledge, Fourier examination, isolating, upgrade, and numerical mix 2-D and 3-D representations capacities with respect to envisioning data, Apparatus for building custom graphical UIs,

Capacities with regards to fusing MATLAB based estimations with outside applications and tongues, for instance, C, C++ and so forth.

The MATLAB tongue is an unusual state lingo with control stream enunciations, limits, data structures, input/yield, and challenge arranged programming features. The available libraries are tremendous aggregation of computational estimations from basic limits, for instance, number juggling and trigonometric abilities to complex limits, for instance, cross section activities and Fourier changes.

In this examination work, we used the Simulink add-on gadget to import Xilinx square set library. In like manner every so often, we used MATLAB to make source codes for memory outline period to deal with data position issue for on-chip memories.

### **C-based Design Tools**

Writing in C dialect has been the customary approach for DSP processors and DSP calculations. This is an option way to deal with utilizing MATLAB coding. This is chiefly because of the way that there are a few outline instruments that can be utilized to produce equipment depiction of these product programs. These devices are getting to be plainly more brilliant to gather the parallelism characteristic to the C code and subsequently, they make it less demanding to make the move from programming to equipment stages. There are numerous varieties for these product apparatuses. The perfect case is to have the capacity to change over ANSI-C to equipment portraval dialects, for example, HDL that are characteristic stage to make equipment. However this is not a completely robotized prepare yet and there is a considerable measure of manual tweaking to the code expected to make it possible for equipment execution. Tragically there is no standard for this situation and each apparatus supplier requires the clients to utilize their own dialect develops and take after their own linguistic structure. Then again, the equipment code created relies on upon the objective stage and again every instrument maker gives its own library to various equipment stages. The thought behind every one of these devices is to make equipment stages accessible to application developers by raising the deliberation level from equipment to programming calculations. There are two vital groupings among all these toolsets: Open standard, for instance, SystemC lingos and the C-toHDL tongues that are prepared for making HDL for either a specific hardware or an insipid gear arrange. Instances of such gadgets are Handle-C, Catapult, et cetera.

SystemC, described by the Open SystemC Initiative (OSCI), relies upon event driven amusement scheme. It empowers the originators to copy synchronous systems using C++ language structure. SystemC methods can pass on in a reenacted steady condition, using indications of the extensive number of data sorts offered by C++. In a couple of respects, SystemC copies the parallelism embedded in the hardware depiction tongues, for instance, VHDL and Verilog, anyway it is up 'til now portrayed as a structure level showing lingo. SystemC fuses HDL components, for instance, clock cycle exactness, dynamic showing, multi-regard basis, delta cycles, assurance work, et cetera. SystemC empowers the engineers to describe modules essentially like HDL tongues and it sets up the correspondence among modules through ports and the demand that is portrayed through the chain of significance. In like manner, strategies are the essential correspondence segments and they are on the whole concurrent. The trades among modules are either by methods for signs or transports/FIFOs.

In case of C-to-HDL mechanical assemblies, there are resemblances and differences among each one of these gadgets. The explanation behind this territory isn't to introduce/delineate these devices. The ordinary property to each one of these instruments is that they all undertaking to automate the methodology of the change of an item computation, for instance, C-based framework to a gear based arrangement, for instance, HDL. This strategy isn't regardless totally robotized and there is reliably a need to manual tweaking of the code with a particular true objective to transform it for hardware amalgamation.

### **II. CONCLUSION**

The lion's offer of C-to-HDL based gadgets attempt to be everything to everyone. In most of the cases, these devices disregard to give comes to fruition that are close to the hand coded plans. Thusly, it is basic to receive a more drew in methodology by concentrating on specific figuring's that are more gainful either for range or execution.

2018

The ability to make applications totally in an irregular state vernacular, for instance, C and have the gadget distribute plot over the FPGA and perform valuable affirmation is amazingly charming. Further, in light of the way that the blueprint of the item and gear is so immovably coupled, the last execution is fundamentally more convoluted.

Hardware fashioners try to upgrade two thinks about plans: zone and execution. In case of FPGA execution, the zone contains most of the configurable method of reasoning passages. Prevalent blueprints make intense use of the available space on a chip to do errands in parallel. The space prerequisite is one new troublesome most extreme that is constrained on a C-based gadgets. Having the ability to fit delivered anticipates chips without wasting space is fundamental for these procedures to be productive.

Timing and tickers are in like manner other basic thinks about execution of hardware systems. Ideally, every part in a gear device is being utilized as much of the time as possible to deal with the most data and achieve the best execution. When working at a higher consideration level, it is difficult to show the arranging of individual system parts while keeping the appearance set up. Or maybe, timing decisions ought to be moved to a lower consultation layer. The decisions will be made thus in perspective of sets of precepts that may give perfect courses of action.

One of the drawbacks of C-based blueprint approach is the loss of fine grained control over the resulting gear. In particular conditions, originator may need to roll out direct improvements, for instance, adding registers to the data and yield of an estimation or pipelining a data path. These sorts of fine grained changes are not viably bestowed to the compiler. Another limitation is that it is extraordinarily difficult to profitably execute control method of reasoning in the pipeline.

Another burden of C-based arrangement approach is the place a settled repeat is required in part of a diagram. The ability to time the method of reasoning at a pined for rate is one of the essential segments of FPGAs. If the repeat of task ought to be settled to support trustworthy correspondence with various resources, it may not be viably passed on to the compiler.

C-based layouts are not for the most part an exchange for HDL based plans. Hardware sections that are shown in the assistant model of an arrangement are not easily delineated in, nor successfully reasoned from, the C tongue. There is constantly a necessity for capable figurings to complete works especially with respect to FPGA execution. This is essentially a direct result of the way that the region.

#### REFERENCES

- C. Papadimitriou, K. Steiglitz, "Combinatorial Optimization, Algorithms and Complexity", Prentice-Hall, inc., 1982. [1].

- T. H. Cormen, C. E. Leiserson, R. L. Rivest, C. Stein. "Introduction to Algorithms". Mc Graw Hill. 2001. [2].

- [3]. F. J. Kurdahi and A. C. Parker. Real: A program for register allocation. In DAC, 1987.

- [4]. K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand. Leakage current mechanisms and leakage reduction techniques in deepsubmicrometer CMOS circuits. Proceedings of the IEEE, 91(2), Feb. 2003.

- R. A. Iltis, S. Mirzaei, R. Kastner, R. E. Cagley, and B. T. Weals, "Carrier Offset and Channel Estimation for Cooperative MIMO [5]. Sensor Networks," IEEE Global Telecommunications Conference (GLOBECOM), 2006.

- J. N. Laneman and G. W. Wornell, "Distributed space-time-coded protocols for exploiting cooperative diversity in wireless [6]. networks," IEEE Transactions on Information Theory, vol. 49, pp. 2415-25, 2003.

- C. Shuguang, A. J. Goldsmith, and A. Bahai, "Energy-efficiency of MIMO and cooperative MIMO techniques in sensor networks," [7]. IEEE Journal oSelected Areas in Communications, vol. 22, pp. 1089-98, 2004.

- T. Aboulnasr and K. Mayyas, "A robust variable step-size LMS-type algorithm: analysis and simulations," IEEE Transactions on [8]. Signal Processing, vol. 45, pp. 631-9, 1997.

- Z. Guo, H. Liu, Q. Wang, and J. Yang, "A Fast Algor ithm of Face Detection for Driver Monitoring," In Proceedings of the Sixth [9]. International Conference on Intelligent Systems Design and Applications, vol.2, pp.267 - 271, 2006.

- [10]. M. Yang, N. Ahuja, "Face Detection and Gesture Recognition for Human-Computer Interaction," The International Series in Video Computing, vol.1, Springer, 2001. [11]. Z. Zhang, G. Potamianos, M. Liu, T. Huang, "Ro bust Multi-View Multi-Camera Face Detection inside Smart Rooms Using Spatio-

- Temporal Dynamic Programming," International Conference on Automatic Face and Gesture Recognition, pp.407-412, 2006. W. Yun; D. Kim; H. Yoon, "Fast Group Verificat ion System for Intelligent Robot Service," IEEE Transactions on Consumer Elect

- [12]. ronics, vol.53, no.4, pp.1731-1735, Nov. 2007.

- V. Ayala-Ramirez, R. E. Sanchez-Yanez and F. J. Montecillo-Puente "On the Application of Robotic Vision Methods to [13]. Biomedical Image Analysis," IFMBE Proceedings of Latin American Congress on Biomedical Engineering, pp.1160-1162, 2007.

- [14]. P. Viola and M. Jones, "Robust real-time object detection," International Journal of Computer Vision, 57(2), 137-154, 2004.

- [15]. Y. Freund and R. E. Schapire, "A Decision-Theo retic Generaliztion of On-Line Learning and an Application to Boosting," Journal of Computer and System Sciences, no. 55, pp. 119-139, 1997.

Mohd.Qutubuddin "Data Placement Algorithm For Power Consumption Reduction in Field Programmable Gate Array "American Journal of Engineering Research (AJER), vol. 7, no. 09, 2018, pp. 132-140 \_\_\_\_\_

www.ajer.org