# American Journal of Engineering Research (AJER)2015American Journal of Engineering Research (AJER)e-ISSN: 2320-0847 p-ISSN : 2320-0936Volume-4, Issue-12, pp-95-100www.ajer.orgResearch PaperOpen Access

## Efficient carry skip Adder design using full adder and carry skip block based on reversible Logic

Varun Pratap Singh<sup>1</sup>, Shiv Dayal<sup>2</sup>, Manish Rai<sup>3</sup>

<sup>1</sup>M.Tech. Student Uttarakhand Technical University Dehradun, Uttarakhand, India <sup>2</sup>Prem Prakash Gupta Institute of Engineering, Bareilly, Uttar Pradesh, India <sup>3</sup>Dept. Of Electronics & Communication Engineering MJP Rohilkhand University, Bareilly, Uttar Pradesh,

India

**Abstract:** In recent years, Reversible Logic is becoming more and more prominent technology having its applications in Quantum Computing, Nanotechnology, and Optical Computing. Reversibility plays an important role when energy efficient computations are considered. In this paper, binary full Adder with Design I and Design II are proposed. The performance analysis is verified using number of reversible gates, Garbage input/outputs, delay, number of logical calculations and Quantum Cost. According to the suitability of full adder design I and design II carry skip adder block is also constructed with some improvement in terms of delay in block carry generation. It is observed that Reversible carry skip Binary Adder with Design II is efficient compared to Design I.

Keywords-Fenyman gate, Fredkin gate, Reversible carry skip adder, Garbage Input/output, Quantum Cost

#### I. INTRODUCTION

#### 1.1 Reversible logic

Reversible computing was started when the basis of thermodynamics of information processing was shown that conventional irreversible circuits unavoidably generate heat because of losses of information during the computation [5]. The different physical phenomena can be exploited to construct reversible circuits avoiding the energy losses. One of the most attractive architecture requirements is to build energy-lossless small and fast quantum computers.

A Reversible circuit/gate can generate unique output vector from each input vector, and vice versa, i.e., there is a one to one correspondence between the input and output vectors. Thus, the number of outputs in a reversible gate or circuit has the same as the number of inputs, and commonly used traditional NOT gate is the only reversible gate. In digital design energy loss is considered as an important performance parameter. Part of the energy dissipation is related to non-ideality of switches and materials. Landauer's [1] principle states that irreversible computations generates heat of K×Tln2 for every bit of information lost, where K is Boltzmann's constant and T the absolute temperature at which the computation performed. Bennett [2] showed that if a computation is carried out in Reversible logic zero energy dissipation is possible, as the amount of energy dissipated in a system is directly related to the number of bits erased during computation.

Since adders, subtractors [11], multipliers [8] are the important blocks for the computation and if these are designed using reversible gates, information loss in computation can be prevented up to the extent of feasibility of circuit based on reversible logic.

#### 1.2 Carry skip adder

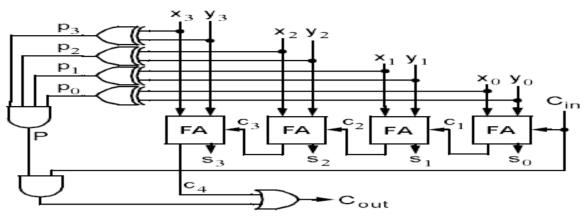

In traditional carry skip adder design an adder block of multiple full adders is constructed. These adder blocks along with carry skip block can be combined to make a carry skip adder to add any number of binary bits.

This adder block receives input carry signal and provides output carry signal. This input carry signal may ripple through each stage of the adder block and appear at the output or it can be predicted by using carry skip block. The carry skip block predicts the intermediate carry output of each stage (full adder) of the adder block on the basis of a carry propagate signal. If carry propagate signal of first stage is one input carry propagate to next stage (full adder) as well as if all the propagate signals are one the input carry is propagated to the output. If any or all propagate signal is zero, input carry signal is not transferred to the output in this case the carry generated

after addition process in last stage is transferred to the output. The propagate signal of each stage in adder block is connected to an AND gate to provide block propagate signal .Now this block propagate signal is combined with the carry output of final stage by using an OR gate to generate final carry output. Figure 1 shows the 4 bit carry skip adder block.

The carry skip worst case delay is observed when the carry generated in very first full adder, ripples through each full adder stage in first block. Thus carry output generated by the first block skips all the intermediate blocks and then it ripple through the full adder stages of the last block[6].

Figure1

There are many reversible logic gates to perform reversible operation. These gates can be used to achieve desired output and optimization of the circuit. To achieve optimization in reversible circuit one should not allow any Fan-out and Loops or feedbacks along with this Garbage outputs, delay and quantum cost should be minimized. These reversible gates can perform various operations in different input conditions. This paper includes 2 basic reversible gates which are as follows.

#### 2.1 Feynman(F) / CNOT Gate

The Fenyman gate is also called Controlled NOT (CNOT) gate it is 2 inputs and 2 gates as shown in Figure 2. This gate maps the input  $(X_1, X_0)$  to output  $Y_1 = Y_0 \quad Y_0 = X_1 \bigoplus X_0$  Quantum Cost of Fenyman gate is one [8]. It can also be used to generate fan out signal by keeping one input to ground according to Figure 3.

### 2.2 Fredkin Gate (FG)

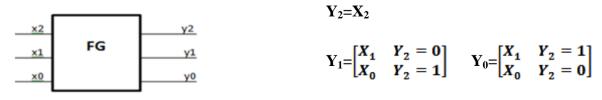

The Fredkin gate shown in Figure 4 is a Reversible  $3\times 3$  gate which maps inputs  $(X_2, X_1, X_0)$  to outputs  $Y_2 = X_2$ ,  $Y_1 = X_2 X'_1 + X_2 X_0 Y_0 = X_2 X'_1 + X_2 X'_0$ . Its Quantum cost is 5[8]. The FG can be used to choose any one of the 2 inputs by applying control signal.

Figure4

www.ajer.org Page 96

2015

2015

The FG gate can also be used to create the inverse and fan out function as in Figure 5 [4]. 2 input AND gate can be generated by grounding one terminal as in Figure 6[4]. The 2 input OR gate can be generated by tying one terminal of FG to supply voltage according to Figure 7. Higher order AND and OR logic can be realized by using FG arranged in Binary tree .A B bit requires B-1 FGs. An input passes a maximum of  $log_2 N$  FGs.

#### **III.PROPOSED MODEL**

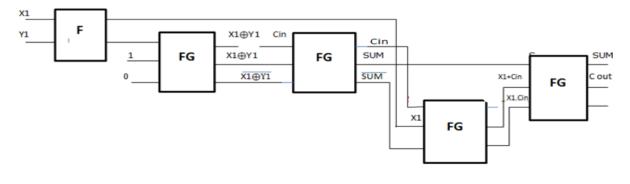

The Reversible gates such as F and FG are used to construct Design I and Design II full Adder. These design are applied to make carry skip adder. Further some delay improvement is also done in carry skip block by determining the state of each propagate signal one by one.

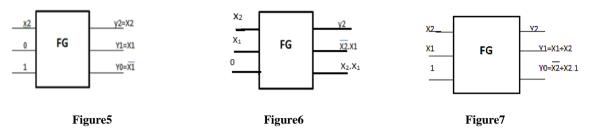

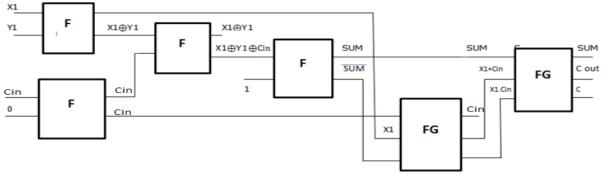

#### 3.1 Design I

This design shown in Figure 8 represents one bit full adder which includes one fenyman gate (F) and 4 fredkin gate (FG). Fenyman gate provides the XOR operation of x1 & y1. The first FG is used to generate 2 signals x1 $\oplus$  x2 and complement of X<sub>1</sub> $\oplus$ X<sub>2</sub>. further if C<sub>in</sub> is one the sum is X<sub>1</sub> $\oplus$ X<sub>2</sub> and if C<sub>in</sub> is 0 sum is  $\overline{X_1} \oplus \overline{X_2}$ . In each case sum and its complement appears at the output of this FG. On the basis of these signals, it can be decided that the value of C<sub>out</sub> is x1+C<sub>in</sub> and X1.C<sub>in</sub>. The total delay in generation of sum signal appears to be one F and 4 FG delay but as in [6] sum bit is the control bit to the 4th FGs hence the delay becomes to be equal to 3 FGs delay. The propagate signal is generated after the one F and one FG delay. This is faster than the design in [6].C<sub>in</sub> is control bit in one FG but it transferred at the output after 2 FG delay , since it depends upon the sum and its complement hence total delay in generating C<sub>out</sub> is one F and 4 FG. There are 2 constant input 3 garbage output and total quantum cost 21 along with total transistor count in design 22where design of fenyman gate includes 6 transistors and transistors.

#### Figure8

#### 3.2 Design II

As shown in Figure 9 proposed design II, 4Fs and 2 FGs are used. The sum is generated after 2 Fenyman gate and its complement is generated by using 1 fenyman gate with 1 input at logic 1. The propagate signal is generated after 2 F gate. Similar to design I carry is generated after sum signal hence the delay in  $C_{out}$  generation is 3 Fs and 2 FGs. Quantum cost of the design is 14. The garbage outputs are 3 and constant inputs are 2.

#### Figure9

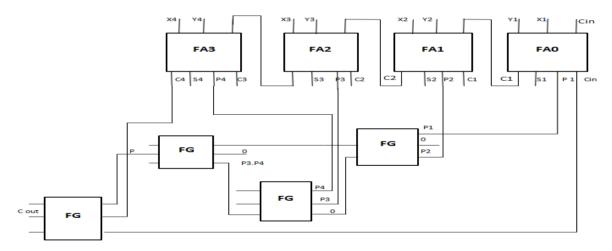

#### 3.3 Reversible 4bit carry skip Binary Adder

The Figure 10 shows the circuit of carry skip adder block to add 4 binary bits. Add operation is performed by full adder due to any one of design I and design II. The AND -OR gate of carry skip block of Figure 2 is replaced by the fredkin gate carry skip logic. In this circuit instead of performing AND operation the fredkin gates provide decision making one by one to each carry propagate signal of each full adder. If first propagate signal is one, second propagate signal is examined and when it appears logic 1, AND operation is performed between last two propagate signal. Thus this design can avoid the delay in AND operation when either first or second or both propagate signals are 0.The total quantum cost of carry skip adder block for 4-bit adding operation is 76.The constant inputs are 11 and garbage bits are 19.

#### Figure10

To construct N bit adder these full adder block of B number of bit can be used. For worst case delay in output carry ( $C_{out}$ ) generation it can be considered that the carry ripples in first and last B bit adder block and in all remaining B bit adder block delay in carry skip block is considered. In carry skip block worst case delay can be considered that all the propagate signals are one so delay of each FG in carry skip block can be considered. Total delay in carry generation in first and last B bit block is 2B per FG of carry transfer, delay of 2F in XOR operation of first two bit in each adder and carry of an adder stage also depends upon sum of previous stage so B F delay is included for final block carry generation. Hence total delay in first block is 2B FG + (B + 2)F as well as Delay in carry skip block is  $\{N/B\} - 2\}$  **3FGs**.

Hence worst case delay can be given as  $T_{Carry} = 2{3B FG + (B + 2)F} + {(N/B) - 2} 3FG$

#### **IV.RESULTS**

#### 4.1 Reversible Full Adder

Since number of transistor used in fenyman gate are 6 and transistor implementation of fredkin gate uses 6 transistors so the table 1 is sufficient to compare both the design.

www.ajer.org Page 98

| Sr.No | Design | Quantum cost | No. Of Transistor | Garbage output | Constant input |  |

|-------|--------|--------------|-------------------|----------------|----------------|--|

| 1     | Ι      | 21           | 36                | 3              | 2              |  |

| 2     | II     | 14           | 36                | 3              | 2              |  |

#### Table I

#### Table II

| Sr.No. Design Carry delay |   | Carry delay | Propagate signal Delay | Sum Delay |  |

|---------------------------|---|-------------|------------------------|-----------|--|

| 1                         | Ι | 1F+4FG      | 1F+1FG                 | 1F+2FG    |  |

| 2                         | Π | 3F+2FG      | 2F                     | 3F        |  |

#### 4.2 Reversible 4-bit carry skip Adder

The reversible carry skip full adder block for 4 bit is designed using the design II and some improvement in carry skip calculation is also done. The carry skip block receives first propagate signal P1 and if this signal is one the propagate signal P2 is examined otherwise block propagate signal is set to logic zero value. The product of propagate signals P3 and P4 is taken on the basis of P1 and if all the propagate signals are one the block propagate signal is generated. On the basis of propagate signals the decision of carry output is performed.

#### Table III

| Sr.No | Design                  | Quantum cost | No. Of Transistor | Garbage output | Constant input |

|-------|-------------------------|--------------|-------------------|----------------|----------------|

| 1     | 4 bit- carry skip Adder | 76           | 152               | 19             | 10             |

#### Table IV

| Sr.no. | Design                  | Carry(worst case)                       | Propagate signal |  |

|--------|-------------------------|-----------------------------------------|------------------|--|

| 1      | 4 bit- carry skip Adder | $2{3B FG + (B + 2)F} + {(N/B) - 2} 3FG$ | 2F               |  |

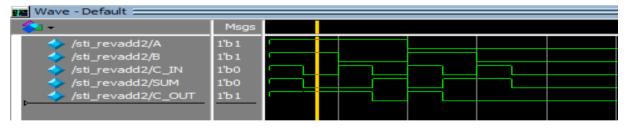

#### 4.3 Simulation

Figure 11 shows the simulation waveform for each input combination of proposed full adder design I using Modelsim PE student edition 10.4

Figure11

Corresponding to proposed full adder design II the simulation waveform is shown in Figure 12.

| Wave - Default   |      |             |   |  |  |  |

|------------------|------|-------------|---|--|--|--|

| 😜 -              | Msgs |             |   |  |  |  |

| Isti_revadd/A    | 1'b1 | · · · · · · |   |  |  |  |

| Isti_revadd/8 🍫  | 1b1  |             | 1 |  |  |  |

| /sti_revadd/C_IN | 1°b0 |             |   |  |  |  |

| /sti_revadd/SUM  | 1'b0 |             |   |  |  |  |

| /sti_revadd/C4   | 1b1  |             |   |  |  |  |

#### Figure12

Carry skip adder simulation result is shown in Figure 13, it is clear that when the block propagate signal (PR) is one, carry input (C\_IN) propagates to the carry output (C\_out) otherwise the ripple carry (C4) will be the carry output.

💶 Wave - Default 🗆 Msgs /carryskipadder0 tb/A (4b0001 /4b0010 /4b1101 /4b010 /4b0101 /4b0101 /4b0110 /4b1111 /4b1000 /4b1001 +/carryskipadder0\_tb/B 4'b1000 4'b0010 14'b1000 14'b0010 (4b1001 4b1001 4 4 b0000 4 4 b0111 4 4 b0110 + /carryskipadder0\_tb/C\_IN carryskipadder0\_tb/SUM 4b1101 (4b1010 (4b1100 (4b0000 (4b1101 4b0111 4b0000 4b1111 4b0000 4b1111 +carryskipadder0\_tb/C\_OUT 1'b0 carryskipadder0 tb/PR /carryskipadder0\_tb/C4

#### Figure13

#### **V. CONCLUSIONS**

Design I and design II both include the basic calculation of AND, OR and EXOR gate using reversible logic. The garbage count, number of transistor and delay are same for both the design but design II is better in point of view of quantum cost. The carry skip block also has some delay improvement over existing design because it checks the propagate signal of each full adder one by one hence reduces the delay in further calculations. The garbage output and constant inputs are reduced in carry skip adder block. In future, the design can be extended to any number of bits for Parallel Binary Adder & Subtractor unit and also for low power Reversible ALUs, Multipliers and Dividers.

#### REFERENCES

- [1] R Landauer, (1961) "Irreversibility and Heat Generation in the Computational Process", IBM Journal of Research and Development, vol. 5, no. 3, pp. 183-191.

- [2] C H Bennett, (1973) "Logical Reversibility of Computation", IBM Journal of Research and Development, vol. 17, no. 6, pp. 525-532.

- [3] T Toffoli, (1980) "Reversible Computing", Technical Memo MIT/LCS/TM-151, MIT Lab for Computer Science.

- [4] E.Fredkin and T. Toffoli, "conservatie logic", Int. J. theoretical physics vol.21, nos 3-4, pp.219-253, 1982.

- [5] C H Bennett, (1998) "Notes on the History of Reversible Computation", IBM Journal of Research and Development, vol. 32, pp. 16-23.

[6] J.W. Bruce, M.A.Thorton, L.Shivkumaraiah, P.S.Kokate and X. Li, "Efficient adder circuit based on a conservative Logic gate "Proceedings of the IEEE Computer Society Annual Symposium on VLSI (ISVLSI.02) 0-7695-1486-3/02.

- [7] Hafiz Md. HasanBabu et al, "Synthesis of full adder circuit using reversible logic "VLSI Design, 2004. Proceedings. 17th International Conference.

- [8] HimanshuThapliyal and M B Srinivas,(2006) "Novel Design and Reversible Logic Synthesis of Multiplexer Based Full Adder and Multipliers", Forty Eight Midwest Symposium on Circuits and Systems, vol.2, pp. 1593 – 1596.

- [9] Himanshu Thapliyal and A.P. Vinod, "Design of Reversible Sequential Elements With Feasibility of Transistor Implementation", Circuits and Systems, 2007. ISCAS 2007. IEEE International Symposium on, 625-628.

- [10] H Thapliyal and N Ranganathan, (2010) "Design of Reversible Latches Optimized for Quantum Cost, Delay and Garbage Outputs", Proceedings of Twenty Third International Conference on VLSI Design, pp. 235-240.

- [11] Jaspreetkaur and Harpreetkaur, "synthesis and designing of reversible adder/subtracter circuit", International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, Vol. 3, Issue 4, may 2014.

2015